In conventional linear analog filters, all the internal signal swings are directly proportional to the input signal. In order to meet a given S/N requirement, the noise floor has to be below the smallest signal by the specified amount. Since the maximum possible signal is determined by the power supply, the small signal condition in a conventional filter represents an inefficient usage of the available swing, and gets worse as the dynamic range of the input signals to be handled increases. A better way would be to maintain the internal swings sufficiently above the noise level for all signal levels which necessarily implies a nonlinear processing at the input and the output. i.e. a small signal can be amplified before being fed to the filter so that all the internal swings are still near the maximum, whereas a large signal is fed straight in (sorta like changing gears in a car to change the speed without letting the engine go too slow to sustain ignition or too fast to stay in one piece). Companding is used for the same reason in telephone transmission systems, by using a compressing non-linearity on the transmit side and an expanding non-linearity on the receive side. The situation is a little more tricky with filters because of the presence of elements with memory. If it is done right, companding ought to increase the dynamic range of filters without using extra power, which would not be possible in a "normal" linear filter because larger power is required either to lower the noise floor or to increase the maximum signal swing that can be handled.

Site menu:

Research

Currently, I and my students are working on delta-sigma data converters, nyquist rate data converters, continuous-time filters, RF circuits, and phase locked loops. A common focus to all these areas is the reduction of power dissipation. I am also interested in the pedagogy of circuit design. More details of these activities can be seen from our group's research and publications pages. In the past, during my stay in the industry, I have worked on high speed analog to digital converters, high speed serial links, and adaptive equalization. During my PhD, I worked on large dynamic range analog filters using companding techniques.

Delta-Sigma ADCs

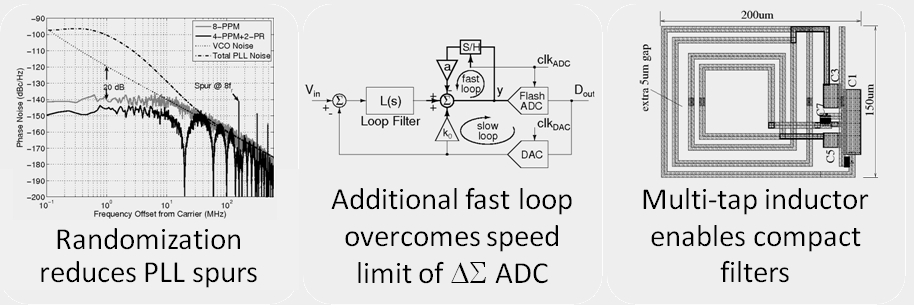

Delta-Sigma ADCs are an attractive alternative to conventional nyquist rate ADCs because they are less reliant on component matching. They require oversampling compared to the nyquist rate for a given bandwidth. Continuous-time Delta-Sigma ADCs operate at a higher maximum speed and consume a smaller power than their discrete-time counterparts. Our work has resulted in a technique for extending the speed limit of Delta-Sigma ADCs in a given process technology. This enables Delta-Sigma ADCs to achieve higher signal bandwidths. We have also worked on the design of a very low power audio Delta-Sigma ADC which has one of the lowest ever reported energy consumption per resolved level, and a technique for using delta-sigma ADCs for sample-by-sample analog to digital conversion without resetting the modulator. The papers describe these ADCs.

- R. S. A. Kumar, N. Krishnapura and P. Banerjee, "Analysis and Design of a Discrete-Time Delta-Sigma Modulator Using a Cascoded Floating-Inverter-Based Dynamic Amplifier," IEEE Journal of Solid-State Circuits, (doi: 10.1109/JSSC.2022.3171790.)

- R. S. Ashwin Kumar and Nagendra Krishnapura, "Multi-Channel Analog-to-Digital Conversion Using a Delta-Sigma Modulator Without Reset and a Modulated-Sinc-Sum Filter," IEEE Transactions on Circuits and Systems I: Regular Papers, (doi: 10.1109/TCSI.2021.3094679).

- R. S. Ashwin Kumar and Nagendra Krishnapura, "Multi-Channel Analog-to-Digital Conversion Techniques Using a Continuous-Time Delta-Sigma Modulator Without Reset," IEEE Transactions on Circuits and Systems I: Regular Papers, doi: 10.1109/TCSI.2020.3013691.

- R. S. Ashwin Kumar, Debasish Behera, and Nagendra Krishnapura, "Reset-Free Memoryless Delta-Sigma Analog-to-Digital Conversion," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 65, no. 11, pp. 3651-3661, Nov. 2018. doi: 10.1109/TCSI.2018.2854707. (paper)

- Debasish Behera and Nagendra Krishnapura, "A 2-Channel 1MHz BW, 80.5dB DR ADC UsingΔΣ Modulator and Zero-ISI Filter," Proceedings of the 40th European Solid-State Circuits Conference, Venice, Italy, Sep. 2014.

- Vikas Singh, Nagendra Krishnapura, Shanthi Pavan, Baradwaj Vigraham, Nimit Nigania, and Debasish Behera, "A 16MHz BW 75dB DR CT ΔΣ ADC compensated for more than one cycle excess loop delay," IEEE Journal of Solid State Circuits, vol. 47, no. 8, pp. 1884-1895, August 2012. (paper)

- S. Pavan, N. Krishnapura, R. Pandarinathan, P. Sankar, "A Power Optimized Continuous-time Delta-Sigma Modulator for Audio Applications," IEEE Journal of Solid State Circuits, vol. 43, no. 2, pp. 351-360, Feb. 2008. (paper)

Ultra-low-distortion amplifiers and filters

Amplifiers and filters with distortion < -100dBc require special circuit techniques including maximizing loop gain without compromising stability, reducing the current driven from the first stage of the opamp, reducing the inherent distortion of the output stage of the opamp, and cancelling distortion due to passive elements.

- Subha Sarkar, Rajat Agarwal, Nagendra Krishnapura, "Bandpass filter and oscillator ICs with THD < -140dBc at 10Vppd for testing high-resolution ADCs," 2023 International Solid-State Circuits Conference, San Francisco, USA, Feb. 2023. doi: 10.1109/ISSCC42615.2023.10067771.

- S. Kumar, R. Goroju, D. K. Bhat, K. S. Rakshitdatta and N. Krishnapura, "Design Considerations for Low-Distortion Filter and Oscillator ICs for Testing High-Resolution ADCs," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 9, pp. 3393-3401, Sept. 2019. (doi: 10.1109/TCSI.2019.2926927).

- Rakshitdatta K. S., Yujendra Mitikiri, and Nagendra Krishnapura, "A 12.5 mW, 11.1 nV/rtHz, −115dB THD, < 1 µs Settling, 18 bit SAR ADC Driver in 0.6µm CMOS," IEEE Transactions on Circuits and Systems II-Express Briefs, vol. 63, no. 5, pp. 443-447, May 2016. (doi: 10.1109/TCSII.2015.2504024).

Estimation of distortion from individual circuit elements

It is easy to simulate the total distortion of a circuit in circuit simulators, but much harder to tell how much distortion is contributed by individual elements. Our technique to determine per-element distortion contributions, described in the paper below, does not require the designer to know the nonlinear models and does not oversimplify the circuit.

- Nagendra Krishnapura and Rakshitdatta K. S., "A Model-Agnostic Technique for Simulating Per-Element Distortion Contributions," IEEE Transactions on Circuits and Systems I-Regular Papers, vol. 61, no. 8, pp. 2219-2228, Aug. 2014. (paper)

Oscillators and phase locked loops

1/f3 phase noise in quadrature oscillators can be minimized by modifying the impulse sensitivity function. Wide tuning range millimeter wave VCOs can be realized using multiple modes with different effective inductances. Randomizing the positions of charge pump current pulses in a PLL breaks their periodicity and redistributes the reference spurs into broadband noise. The paper below describes the analysis of such pulse position modulated signals and simulated results of spur reduction techniques in wideband PLLs.

- Abhishek Bhat and Nagendra Krishnapura, "A Reduced-Area Capacitor-Only Loop Filter With Polarity-Switched Gm for Large Multiplication Factor Millimeter-Wave Sub-Sampling PLLs," IEEE Transactions on Circuits and Systems I: Regular Papers, (doi: 10.1109/TCSI.2021.3096843).

- Abhishek Bhat and Nagendra Krishnapura, "A 25-to-38GHz, 195dB FoMT LC QVCO in 65nm LP CMOS Using a 4-Port Dual-Mode Resonator for 5G Radios," 2019 International Solid-State Circuits Conference, San Francisco, Feb. 2019.

- Abhishek Bhat and Nagendra Krishnapura, "Low 1/f3 Phase Noise Quadrature LC VCOs," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 65, no. 7, pp. 2127-2138, July 2018. doi: 10.1109/TCSI.2017.2782247. (paper)

- Abhishek Bhat and Nagendra Krishnapura, "On-Chip Static Phase Difference Measurement Circuit with Gain and Offset Calibration," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 66, no. 2, pp. 162-166, Feb. 2019. doi: 10.1109/TCSII.2018.2842101. (paper)

- Chembiyan Thambidurai and Nagendra Krishnapura, "On Pulse Position Modulation and its Application to PLLs for Spur Reduction," IEEE Transactions on Circuits and Systems I-Regular Papers, vol. 58, no. 7, pp. 1483-1496, July 2011. (paper)

Continuous-time filters

Long true-time-delays can be realized over wide bandwidths using reflectios from singly-terminated ladder filters. Low-distortion active filters can be realized using current- efficient feedforward-compensated operational amplifiers in the integrators and feedforward current injection in the summing amplifier which typically operates with a smaller feedback fraction. Passive LC ladder lowpass filters can be made compact using a single inductor with multiple taps. The papers below describe these efforts.

- I. Mondal and N. Krishnapura, "Effects of AC Response Imperfections in True-Time-Delay Lines," IEEE Transactions on Circuits and Systems II: Express Briefs, doi: 10.1109/TCSII.2020.3027529.

- Imon Mondal and Nagendra Krishnapura, "A 2-GHz Bandwidth, 0.25-1.7 ns True-Time-Delay Element Using a Variable-Order All-Pass Filter Architecture in 0.13 μm CMOS," IEEE Journal of Solid-State Circuits, 2017. (paper)

- Nagendra Krishnapura, Abhishek Agrawal, and Sameer Singh, "A High IIP3 Third Order Elliptic Filter with Current Efficient Feedforward Compensated Opamps," IEEE Transactions on Circuits and Systems II-Express Briefs, vol. 58, no. 4, pp. 205-209, April 2011. (paper)

- Nagendra Krishnapura, Varun Gupta, Neetin Agrawal, "Compact Lowpass Ladder Filters Using Tapped Coils," 2009 International Symposium on Circuits and Systems (ISCAS), Taipei, Taiwan, 24-27 May 2009. (paper, slides)

Circuits and systems pedagogy

The papers below discuss alternative approaches to introducing negative feedback circuits such as opamps and phase locked loops.

- Nagendra Krishnapura, "Introducing Negative Feedback with an Integrator as the Central Element," 2012 International Symposium on Circuits and Systems (ISCAS), Seoul, South Korea, 20-23 May 2012. (paper, slides)

- Nagendra Krishnapura, "Synthesis Based Introduction to Opamps and Phase Locked Loops," 2012 International Symposium on Circuits and Systems (ISCAS), Seoul, South Korea, 20-23 May 2012. (paper, slides)

Companding filters

Dissertation: Large Dynamic Range Dynamically Biased Log-Domain Filters

This dissertation investigates the enhancement of the dynamic range per unit power consumption of analog filters using dynamic biasing. A technique for realizing dynamically biased log-domain filters while maintaining input-output linearity is presented. This method is much simpler than previously known techniques for realizing large dynamic range filters using syllabic or instantaneous companding. The consequent advantages of the proposed technique are pointed out.

In order to demonstrate the capabilities of the proposed dynamically-biased log-domain filters, a third-order Butterworth filter with a cutoff frequency of 1MHz is designed in a 0.25µm BiCMOS technology. Circuit techniques to ensure proper operation of the filter over a wide range of input currents are presented. With suitable dynamic biasing, the fabricated filter can maintain a THD < 40dB and S/N > 53.7dB for differential input current amplitudes ranging from 3µA to 2.5mA(a range of 58.4dB). In terms of the range of signals that can be handled, the performance is equivalent to that of a conventional filter with a maximum signal to noise ratio of 112dB. The filter draws 575µW from a 2.5V supply in the quiescent condition and 26.1mW with the maximum input amplitude of 2.5mA. The maximum power consumption normalized to the order, the dynamic range, and the bandwidth is 5.9 x 10-20 J, which represents more than an order of magnitude of improvement over existing filters.

The design of a current mode peak detector that can provide the dynamic bias to the filter based on the input signal strength is presented. Satisfactory operation of the peak detector over a range of current amplitudes from 1.4uA to 2.8mA is verified experimentally. The envelope detector in a 0.25µm BiCMOS technology occupies 0.12mm2 and consumes 162.5µW in the quiescent condition. The attack time for a 1:2 increase in the input amplitude is less than 1.2µs and the decay time for a 2:1 decrease in the input amplitude is less than 40µs over the entire range of input amplitudes.

The feasibility of log-domain filtering in standard CMOS processes is verified by an experimental prototype of a 22kHz second-order filter using lateral bipolar transistors and pMOS accumulation capacitors. This filter occupies 0.085mm2 in a 0.25µm CMOS technology, consumes 4.1µW from a 1.5V supply, and has a measured dynamic range of 56.1dB.

The behavior of noise in companding systems is different from that in classical linear systems due to their inherent internal nonlinearity. Methods for analysis and simulation of noise in instantaneous companding processors are presented. Experimental results corroborating the theory are given.